Ubuntu 18が出たので、やりかたを確かめつつまとめ

とりあえずARMで動かすUbuntu18をセットアップするためにLinuxが必要.

日本語の設定が、前よりも簡単になっていた。

Ubuntuの設定から

言語メニューを選択

もう既に日本語化してしまったが、

「インストールされている言語の管理」→「言語のインストールと削除」

で日本語を追加する。

日本語を追加したら、

「メニューとウィンドウの言語」でそれを一番上に持ってくる。

あとは再起動すれば日本語になっている。

fishのインストール

shellにはzshよりもfishをおすすめしたい

sudo apt-add-repository ppa:fish-shell/release-2

sudo apt-get update

sudo apt-get install fish

u-bootのビルド

まずはu-bootをビルドするのに必要なものをインストールする。

fishなら以下をコピペするだけでOK

sudo apt-get -f install

sudo apt-get install fakeroot build-essential kexec-tools

sudo apt-get install kernel-wedge gcc-arm-linux-gnueabi

sudo apt-get install u-boot-tools libncurses5

sudo apt-get install libncurses5-dev libelf-dev

sudo apt-get install asciidoc binutils-dev git

sudo apt-get build-dep linux

sudo sudo apt-get install bc

まずarm gccがバージョン6以上であるかを確認する。

arm-linux-gnueabi-gcc -v

version 7.3.0であった。

ここでversion 6.x 以上出ないと、xilinxのリポジトリの最新のubootのビルドに失敗する。

つぎにxilinxのリポジトリからu-bootをクローンしてくる

git clone https://github.com/Xilinx/u-boot-xlnx

追加。

cd u-boot-xlnx

echo "CONFIG_OF_EMBED=y" >> configs/zynq_zybo_defconfig

これがないと

No valid device tree binary found

とエラーが出る。

ビルド

make ARCH=arm CROSS_COMPILE=arm-linux-gnueabi- zynq_zybo_config

make ARCH=arm CROSS_COMPILE=arm-linux-gnueabi-

でu-bootというのができている。

これをu-boot.elfとリネームしてどこかに置いておく。

(そうしないとNo Execution Address JTAG handoffと出る。

Solved: ZC706 QSPI Boot: FSBL does not hand off to U-Boot - Community Forums)

kernelのビルド

git clone https://github.com/Xilinx/linux-xlnx

いま時点でmasterはkernel 4.x (≧4.9)

(新しいgccではkernel 3.xはビルドできない。)

make ARCH=arm CROSS_COMPILE=arm-linux-gnueabi- xilinx_zynq_defconfig

make ARCH=arm CROSS_COMPILE=arm-linux-gnueabi-

make ARCH=arm CROSS_COMPILE=arm-linux-gnueabi- UIMAGE_LOADADDR=0x8000 uImage

で\arch\arm\bootにuImageができている。

bitファイルをつくる

Zybo [Reference.Digilentinc]

の下の方にZybo Base Systemがある

おそらく初代Zyboがもう作られてないからdeprecatedである。

この中の、\zybo_base_system\source\vivado\hw\zybo_bsd

をVivado 2017.3で新しく保存し直した。

(このままBitstreamを作ろうとしたところ

BTNs_4Bitなどで原因不明のエラーが出たので、

一度AXI-GPIOをすべて消してからIO Plannningで割り当て直したら直った。)

Bitstreamを出す。

File→Export で include bitstreamにチェックを入れてOK

devicetree

引き続きVivadoから

File→Launch SDKを行う。

HDFが自動で読み込まれる。

zybo 割り込み② SDK, devicetree編 - e-tipsmemo

と同じ。

Devicetree generatorを入れる

git clone https://github.com/Xilinx/device-tree-xlnx

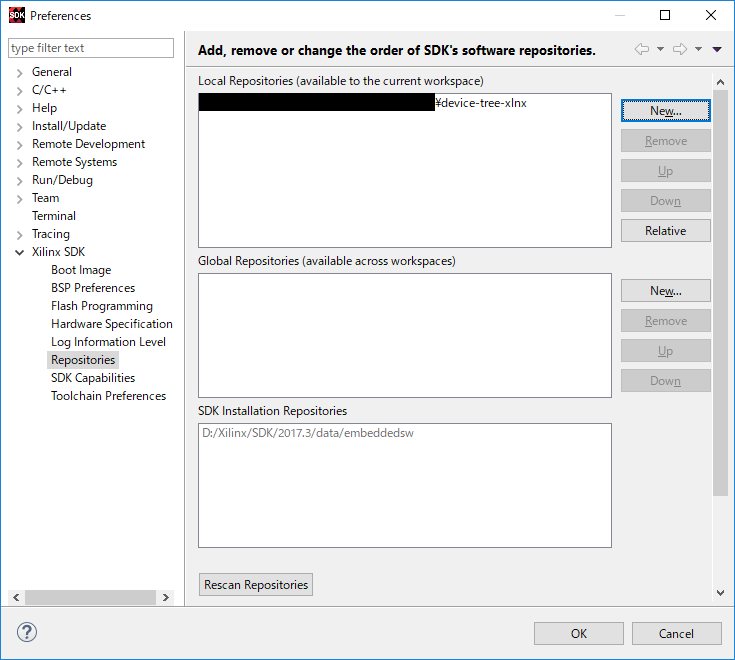

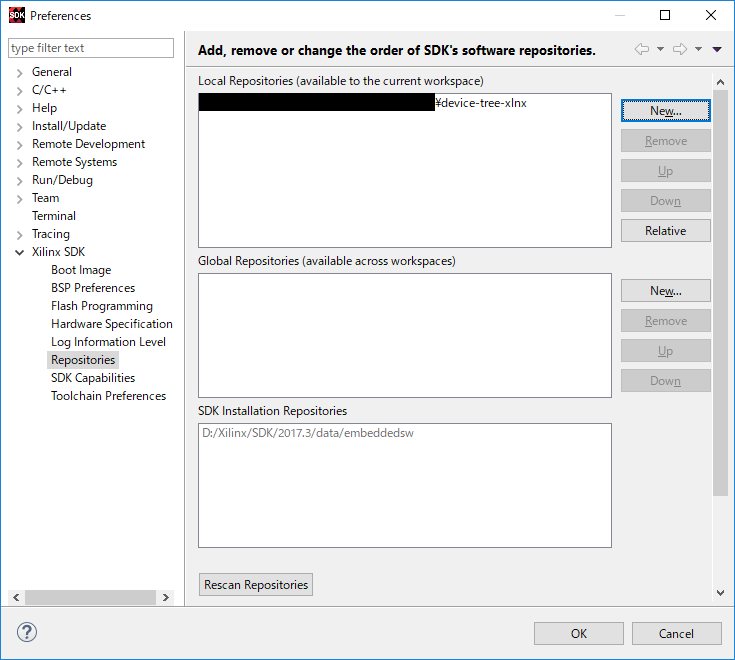

SDKから

Xilinx→Repositoriesで

Newを押すとダイアログが出るので、クローンしたリポジトリを指定する。

OK

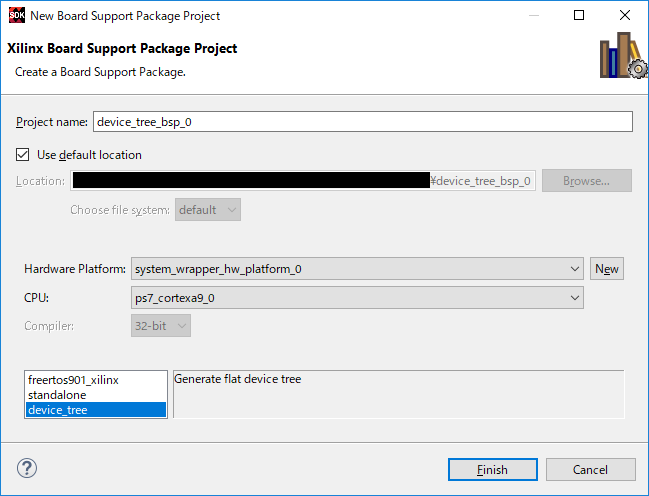

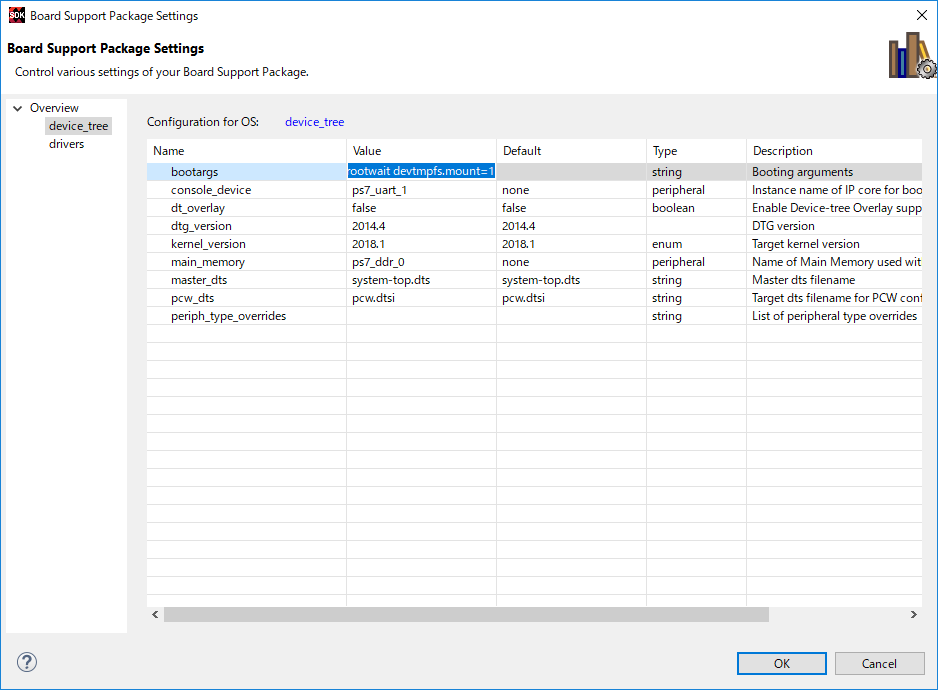

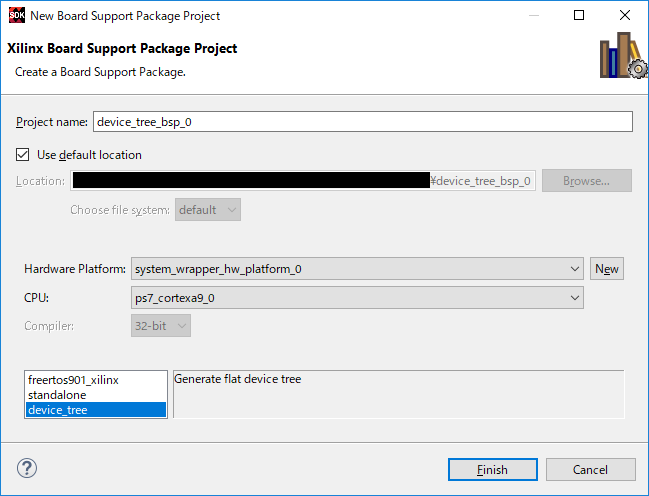

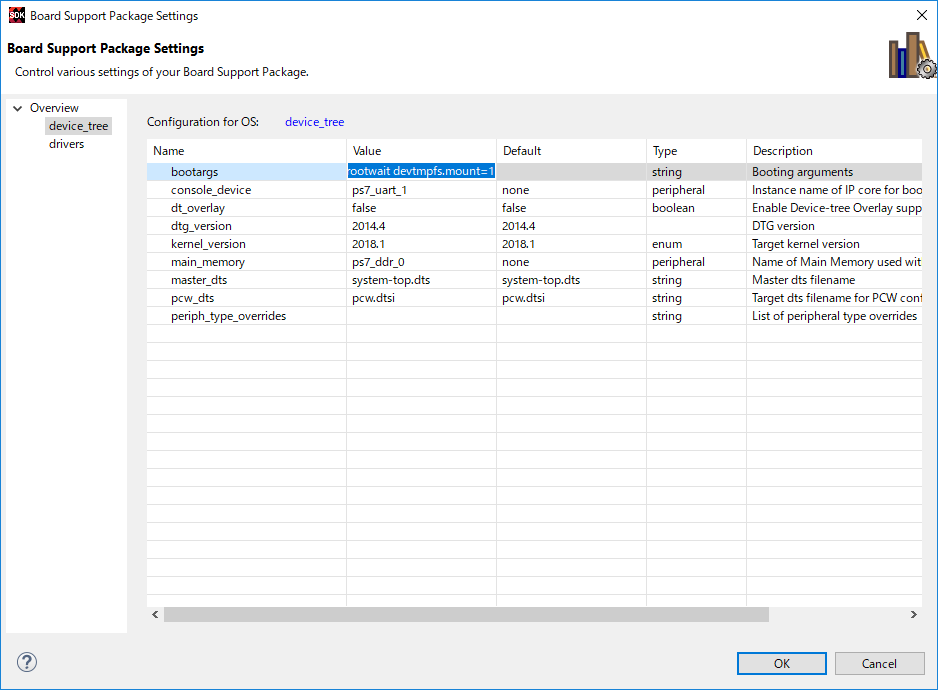

File→New→Board Support Packageで

Board Support Package OSから

device_treeを選択。

bootargsに

console=ttyPS0,115200 root=/dev/mmcblk0p2 rw earlyprintk rootfstype=ext4 rootwait devtmpfs.mount=1

を入れる。

zynq-7000.dtsの

gem0をokayにする。

gem0: ethernet@e000b000 {

compatible = "cdns,zynq-gem", "cdns,gem";

reg = <0xe000b000 0x1000>;

status = "okay";

interrupts = <0 22 4>;

clocks = <&clkc 30>, <&clkc 30>, <&clkc 13>;

clock-names = "pclk", "hclk", "tx_clk";

#address-cells = <1>;

#size-cells = <0>;

};system-top.dtsに

mdio {

compatible= "cdns,macb-mdio";

reg= <0xe000b000 0x1000>;

clocks = <&clkc 30>, <&clkc 30>, <&clkc 13>;

clock-names = "pclk", "hclk", "tx_clk";

#address-cells = <1>;

#size-cells = <0>;

eth_phy0:phy@1 {

compatible = "realtek,RTL8211E";

device_type = "ethernet-phy";

reg = <0x1>;

};

};を追加する。

ここと同じ。

zybo ethernet Ubuntu 17 ipv4 - e-tipsmemo

DTC入れる。

sudo apt-get install device-tree-compiler

コンパイル

dtc -I dts -O dtb -o devicetree.dtb system-top.dts

dtc -I dtb -O dts -o devicetree.dts devicetree.dtb

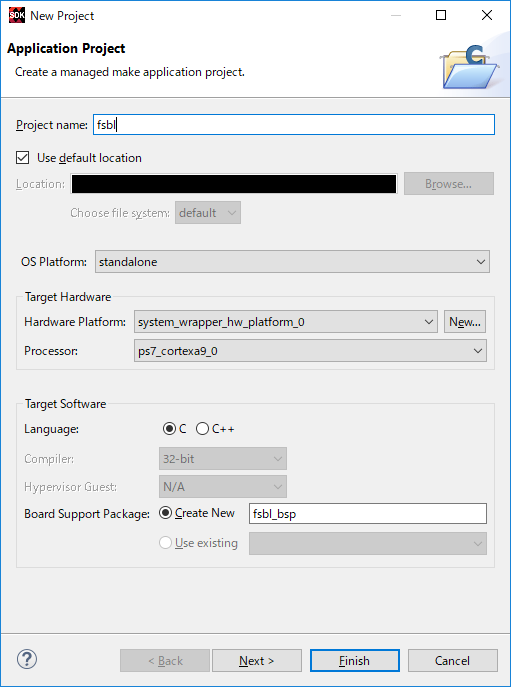

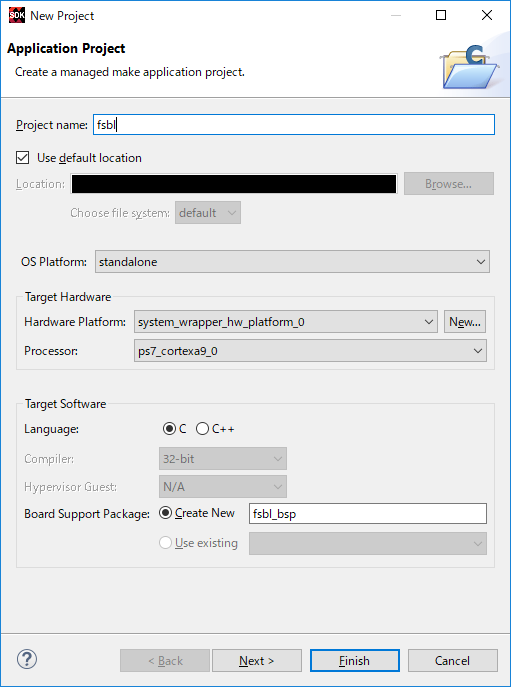

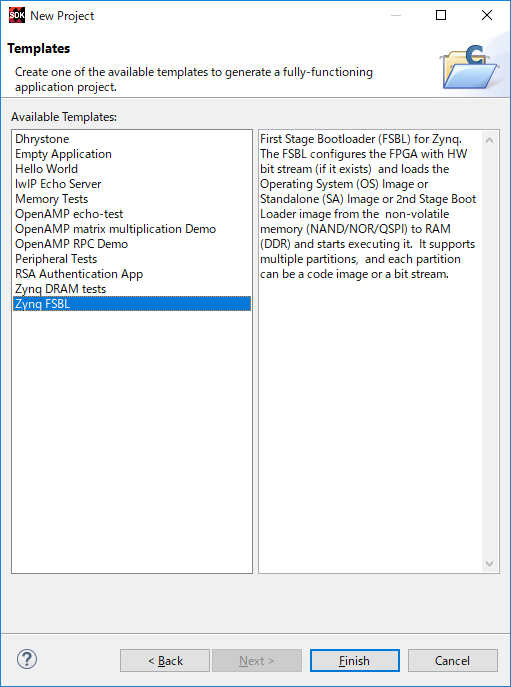

FSBL

SDKで

File→New→Application Proejct

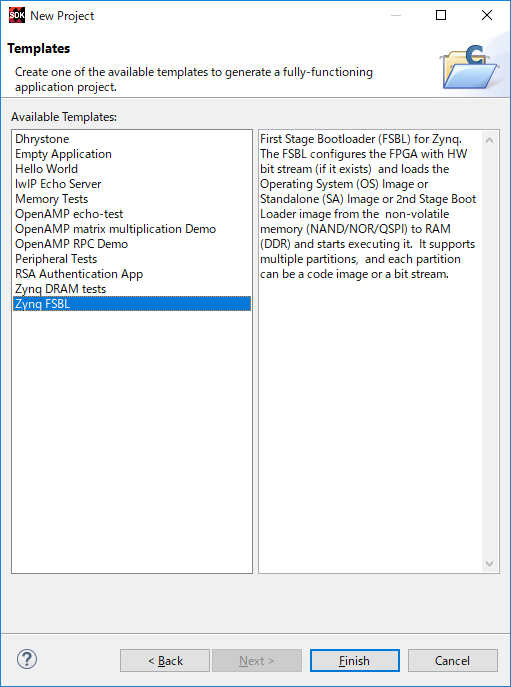

fsbl入れてNextでZynq FSBLを選択。

Finish

\zybo_base_system\source\vivado\SDK\fsbl

のfsbl_hook.c全部をプロジェクトのfsblのsrc/fsbl_hook.cにコピペ。

(bitstreamを作るときにZynqからIICやethernetを出してないとここでエラーがでる。)

fsbl_debug.hに追加

#define FSBL_DEBUG_INFO

ビルドしてfsbl\debug\fsbl.elfがあればOK

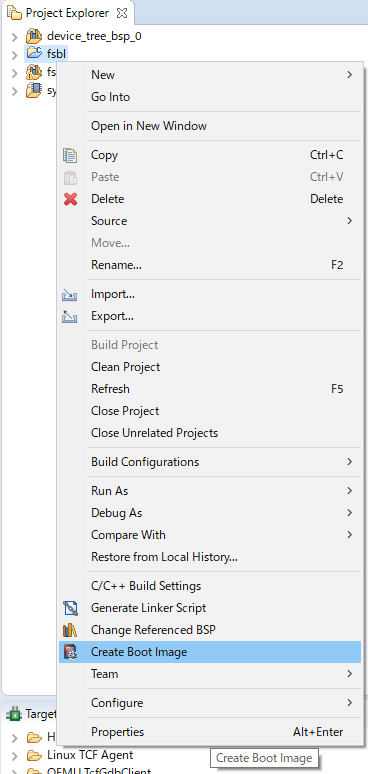

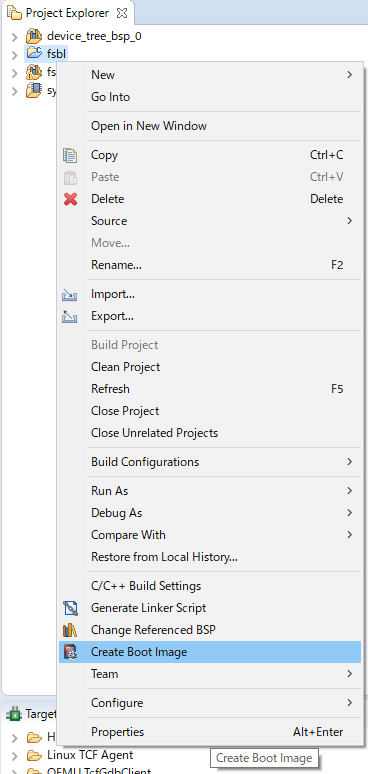

BOOT.binを作る。

から下のAdd→Browse..でu-boot.elfを選択する。

OK