フォーマッター

巷のソフトウェア言語に比べ、HDLのフォーマッターは少ないが、

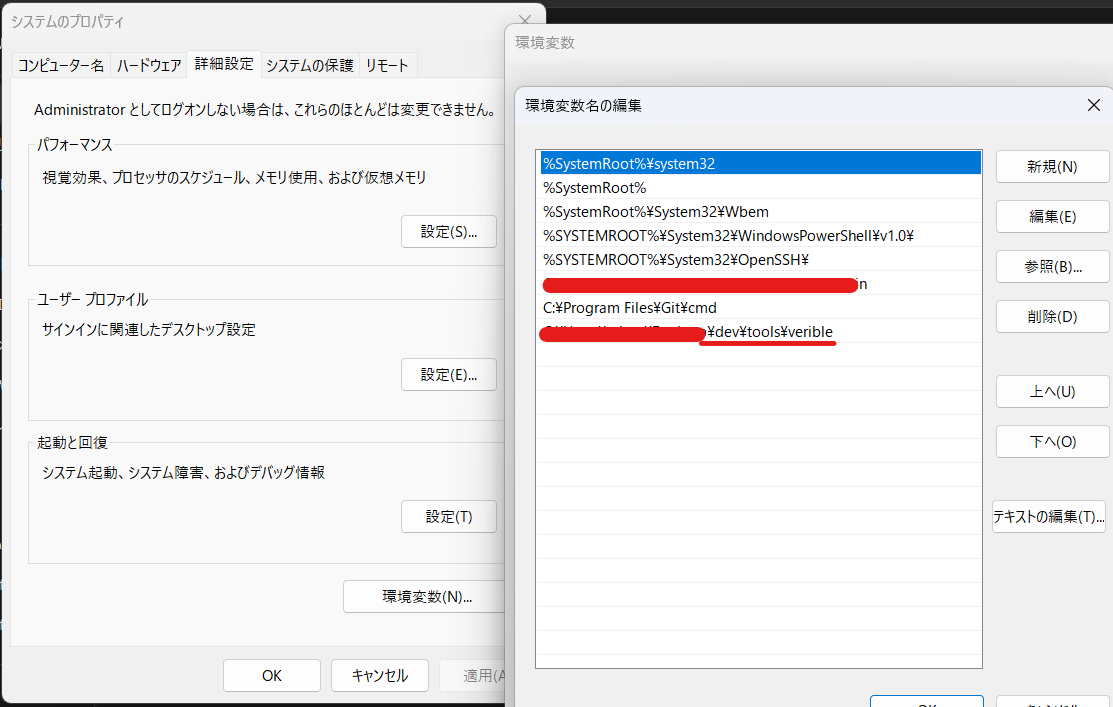

Chipsallianceがフォーマッターをリリースしているので、それを使用する。

Releases · chipsalliance/verible · GitHub

適当な場所に展開し、パスを通す。

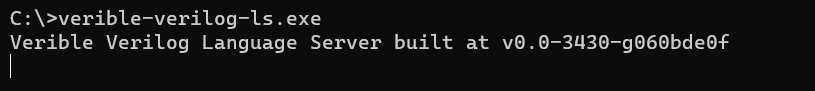

コマンドプロンプトでパスが通ってることを確認

ModelSim

無料のHDLシミュレーターとしてiverilogがあるが、SystemVerilogの文法にどの程度対応しているのかわからないことや、コマンドがちょっと面倒なので、

ModelSimを使用することにした。

ModelSimはIntel版だとかXilinx版だとかQuartus Primeだとかいろいろバンドルが違うようだが、Intelのサイトからそれ単体をダウンロードすることができる。

ModelSim-Intel® FPGAs Standard Edition Software Version 18.1

Starter Editionはライセンスなしで使用することができる。(制限あり)

VScodeの設定

拡張機能に以下を追加する

Verilog-HDL/SystemVerilog/Bluespec SystemVerilog - Visual Studio Marketplace

これはveribleに対応しているらしい。

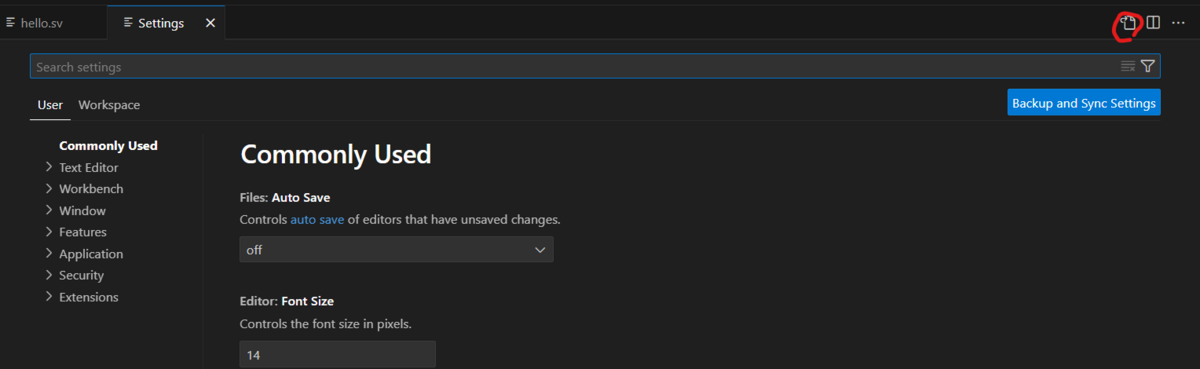

Ctrl + ,

で設定画面を開いたらjson編集モードにして

以下を追加する

"[verilog]": { "editor.formatOnSave": true, }, "[systemverilog]": { "editor.formatOnSave": true, },

これで保存時にsvやvのファイルが勝手にフォーマットされると思う。

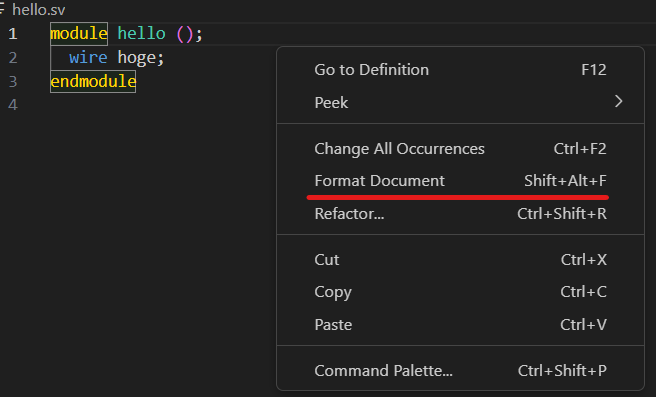

(されないときは、右クリックから一回フォーマットしてやると、治る気がする)

ビルドの構成

VScodeからGUIレスで、svをビルド & シミュレーションしたいので、modelsimのコマンドを呼ぶ。

Shift + Ctrl + B

から呼び出すコマンドを以下のように定義する。

{ // See https://go.microsoft.com/fwlink/?LinkId=733558 // for the documentation about the tasks.json format "version": "2.0.0", "tasks": [ { "label": "vsim", "type": "shell", "command": "./run.bat", "group": { "kind": "build", "isDefault": true } } ] }

サンプルコード

module hello ( clk ); input clk; reg [31:0] count = 0; always_ff @(clk) begin : counter count <= count + 1; end endmodule

`timescale 1ps / 1ps module tb_hello (); reg clk = 0; hello dut (clk); always #1000 clk = ~clk; initial begin $dumpfile("wave.vcd"); $dumpvars(0, tb_hello); repeat (10) @(posedge clk); $stop; end endmodule

run.bat & modules.txt

ModelSimをコマンドから実行するのに必要なコマンドを並べる

run.bat

vlib MODELSIM_LIB vmap MODELSIM_LIB MODELSIM_LIB vlog -work MODELSIM_LIB -f modules.txt vsim -c tb_hello -lib MODELSIM_LIB -do "run -all;quit -f;"

modules.txt

hello.sv tb_hello.sv

ビルドのスクリプトで、modules.txtを毎回生成することもできる気がするが、

そこまでは頑張らない。

Shift + Ctrl + B

で、run.batが実行され、ModelSimが実行され、

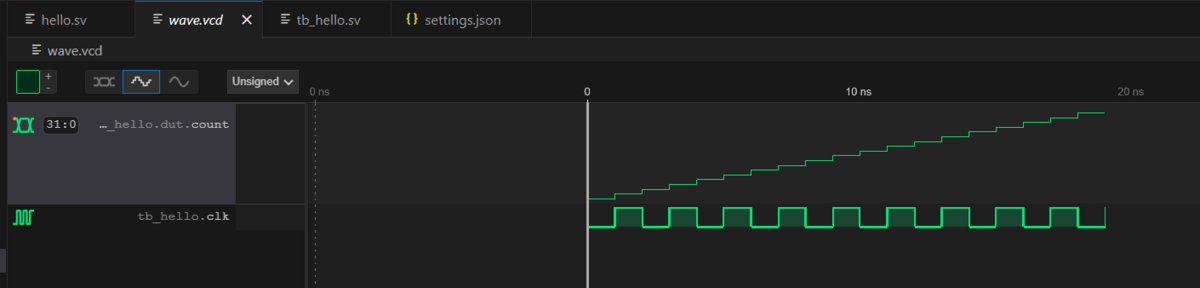

vcd view

VScode上からVCDを見れる。

無料版だと波形表示数に上限がある。

(もっといい波形ビューワーはないか?結局gtkwaveを使っている)

WaveTrace - Visual Studio Marketplace