昔と違って、それなりのスペックのFPGAが実装された評価ボードが、かなり簡単に手にはいるようになっているので、

- スペック

- 開発無料(Vivado webpackで開発できる not ISE)

の点で昔を懐かしみながらまとめてみた。

(面白い評価ボードがあったら、何かを始めてみたいとおもったので)

!!!2021年時点!!!

FPGAボード

純粋にFPGAだけが載っているボードを列挙

KintexとかでもWebpackで開発できるグレードもあるが、多分高いので除く。

HDLを勉強〜とか

Chisel〜とか

CPUつくる〜とかなら

こういうシンプルなボードの方がいい気がする。

Arty A7-35T

Arty A7: Artix-7 FPGA開発ボード メーカーや趣味の方用 (Arty A7-35T)

- メディア: Personal Computers

もっとリソースの多いグレードでArty A7-100T(Artix7 100T)というものもある。

かなりシンプルな拡張性しか持っていないので、7セグとかUSBとかHDMIしたいときは回路を作ってつなげる必要がある。(実装されているUSBmicroAコネクタはSerialとJTAG用)

ボード上のピンヘッダはArduino互換の様に見えるが、物理的な位置が同じなだけであって、電源とかGNDとかは微妙に違った気がしなくもない。(そもそも2列なので、使い勝手悪い、Pmodを使ったほうがいい)

確か、Vivado Design Editionのボード限定&1年限定ライセンスコードも付属していた気がする(Arty A7しか開発できないDesign Edition)

評価ボードには小さいゴム足が付いていた気がする。

Nexys A7

Artix7 50TとArtix7 100Tのグレードがある。

Arty A7との差はUSBと7セグと大量のスイッチ。ボードには足がついてた気がする。

Arty S7

Digilent Arty S7:Spartan-7 FPGAボード メーカーや趣味の方に (Arty S7-25)

- メディア: Personal Computers

Spartan6以上Artix7以下という立ち位置。

リソースはArtix7以下だが、価格も低い。

Artix7とどちらを選ぶかという点では価格、PLLの数やDSPの数、Block RAMの大きさというとこも考える必要もあるかもしれない。

DE0 nano

Cyclone4が乗っている。こちらはTerasicが出しているAltera(intel)のFPGAの評価ボード。昔はDE0とか言うのがあって大きかったしちょっと高かった気がするが、nanoは小さくてよさそう。周辺回路は最低限という感じ。

Quartus Primeという開発環境で行うが基本的なところはVivadoと変わらない気がする。(Quartus 13?以降知らないので)

DE0 CV

Cyclone5が乗っている。値段的にはDE0の後継っぽい?

周辺回路はそこそこだが、右列のボックスピンヘッダ?はあんまりユニバーサル基板フレンドリーじゃない気がする。

基本的にTerasic直販だと学割が効いた気がする。

AlteraはマルツでEP1C3T100C8Nの評価ボードを買ったのが最初で最後だった記憶。

趣味の人たちはみなXilinxを使っているようだ。(なんでだろう)

CPU+FPGAボード

FPGAとArmコアがくっついてる。

HLSでHWアクセラレータ〜とかコンピューティング〜とかだとこっちのほうがいいかもしれない。

Armのところで簡単にLinuxが動くようなサポートになってたりする。

ZynqやUltra Scale MPSocの評価ボードでリーズナブルなもの

Cyclone V SOCもあるが、インテルはあんまり推して無いのかな。

Zybo Z7

Digilent Zybo Z7: Zynq-7000 ARM/FPGA SoC 開発ボード (Zybo Z7-20 SDSoC Voucher)

- メディア: Personal Computers

(前のバージョンはHDMI Sinkの代わりにAnalog RGBが載っていた)

Zynq-7010よりZynq-7020のほうがリソースが多い。

Artix7と違って、これのEth, USB, SDIOあたりは、Armコアのペリフェラルに直接繋がっている。

ネジ穴に足がついてた気がする。

Arty Z7

Digilent Arty Z7: AP SoC Zynq-7000 開発ボード メーカーと趣味者用 Arty Z7-20 with Zynq SDSoC Voucher ホワイト

- メディア: Personal Computers

Zyboの廉価版?

zynq 7010かZynq 7020のグレードもある。

Pmodの代わりにHDMI Sink/Sourceがある。

PYNQ Z1

Arty Z7のピンク色Ver?

細かく見ていないのでArty Z7との違いは分からないが、(USBの向きが違う)

Digilentのストアで学割が効くので、学生でzynqボードがほしいならこれが最安かもしれない。

PYNQ-Z2もあるが別のメーカーが出しているようだ。(オーディオCHIPが乗っていることとラズパイがつながるヘッダーが乗っている。いるか?)

Ultra 96V2

www.avnet.com

ZYNQ UltraScale+(zynqMP)の評価ボードで

Zynq UltraScale + MPSoC ZU3EGを載せている。

Webpackでも開発できるグレード。

TE0802

akizukidenshi.com

これもZYNQ UltraScale+だがUltra 96よりは周辺機器がついていてなんか良さそう。

HDMIじゃないのが残念。

XCZU2CG なのでUltra 96のグレードよりは1個下?

MPSocはCortex A53とCortex A9とMicroblazeが入っている。

LinuxをブートするためにVivadoとは別に、Petalinuxとかいうものをインストールしなければならないのが苦痛(もちろんしなくても出来るかもしれないがとても面倒くさそうだった)

DE1-Soc

www.digikey.jp

AlteraのFPGA-SocでCyclone V Socが乗っており周辺回路も豊富

DE10-nano

www.digikey.jp

昔はなかった気がする。安い。

FPGA(Soc)+α

本当はSDRボードを調べていたのでついでにFPGAボードもまとめただけ。

やっぱりFPGA単体では、それ上で完結してしまう...ということで、SDR方面で探すと、面白いボードもいくつかあったりする。

ADRV9364-Z7020

www.digikey.jp

AD9364というチップがすごくて、割とワイドバンドなTRXをワンチップで乗せている。LVDSが出ててそれがFPGAに直結している。

もう一個上のグレードでAD9361+Z7035という組み合わせがあるがこれはTRXが2x2でMIMOとかもできるのだが、Z7035はWebpackでは開発できない。

このボード単体だと意味をなさなくて、下側につけるキャリアーボードが必要。ピンヘッダもついていていい感じ?

ADRV1CRR-BOB Analog Devices Inc. | RF/IFおよびRFID | DigiKey

とか

ADRV1CRR-FMC Analog Devices Inc. | RF/IFおよびRFID | DigiKey

microSDがついてきた気がするが、Debianがインストールされていた。

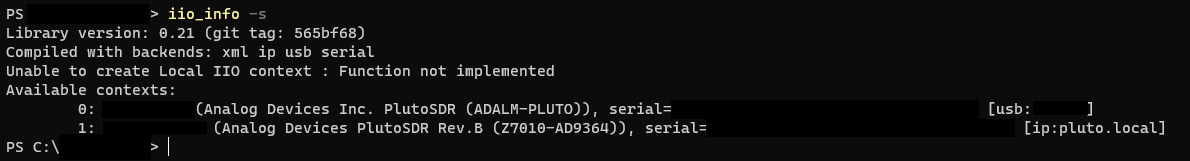

AD9363 + Z7010という構成だとADALM-PLUTOの構成となる。(AD9364はAD9363の選別品らしい?)

ADI ADRV936x System on Module (SOM) SDR [Analog Devices Wiki]

サポートページ

FreeSRP

freesrp.org

さすがにADRVのやつは高いなってなると、Artix7と接続したSDRボードがあった。

拡張性は背の低いコネクタが一つだけ。

USB3.0で接続できるらしい。

アクリル板もある。

LimeSDR

wiki.myriadrf.org

MAX10とTRXチップで構成されているやつ

評価ボードというよりはすでに構成されているものとして、GNURadioで何かを受信しましょうという感じかもしれない。

他にもUSRPというワードで検索すると高いのか安いものがでてくるが、安いほうだとSpartan6で、Vivadoでは開発できないので、除外した。

感想

記事を書き上げてから、こんな記事書くまでもなく、英語で調べればでてくるなと思った。

Cheap FPGA Development Boards | Joel's Compendium of Total Knowledge

それなりの値段でFPGAが買えるし開発環境も無料だし調べれば無料だしいい時代だなと思った。

ただVivadoのインストールで要求する容量が尋常じゃない(Petalinuxとは別)上に、

ビルドで細かいファイルをたくさん作りまくるので、評価ボードよりも大容量SSDとか買ったほうがいい気がする。

Western Digital SSD 1TB WD Blue PC M.2-2280 SATA WDS100T2B0B-EC 【国内正規代理店品】

- 発売日: 2019/06/23

- メディア: Personal Computers