VivadoのIPコアはたくさんあって便利だけども

シンプルな機能を求めるときには、

調べるの面倒とか、微妙に思っていたのと違うと感じることが多々あった気がするので、

仕方ないので自分で書いたものをメモ

BRAM IFにつなげて同じ幅のAXI Streamで連続データを出してくれるようなシンプルなもの。

(DACとかを想定している)

BRAMの出力は遅延を最小にしても1クロック遅く出てくるので、

treadyが下がった時にBRAMへのアドレスを一つ戻す必要があるっぽい。

参考

How to make an AXI FIFO in block RAM using the ready/valid handshake - VHDLwhiz

コード

雑に書いたので使ってないwireが残っている上にコードが見にくい。

いつか綺麗にするかもしれない。

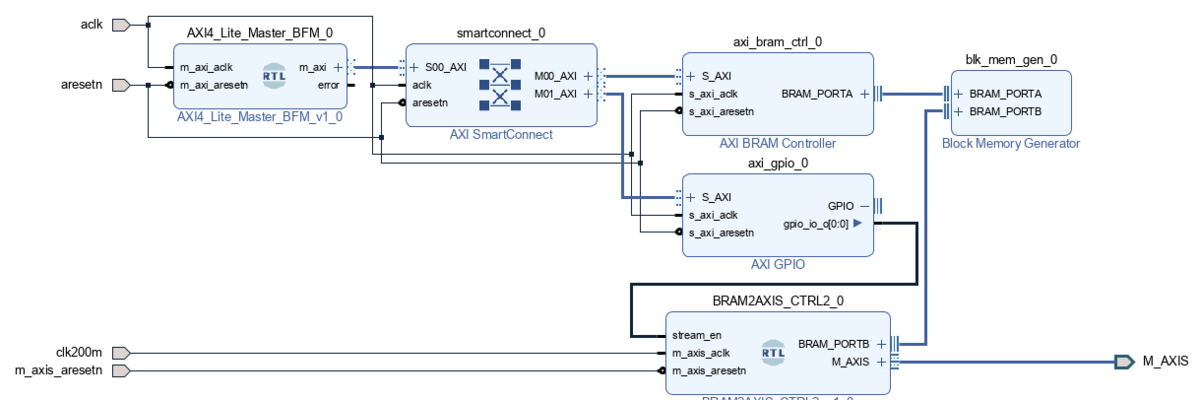

Block Diagramに配置

BRAMを介して、AXIからAXISに変換するついでに幅も変換する

PORTAからはAXI Liteアクセスにしているので32bit幅固定

遅延するようなオプションは全部オフ。

バッファーが必要そうならAXI4-Stream Register Sliceを使うといい気がする。